10+ zynq block diagram

Zynq Workshop for Beginners ZedBoard -- Version 10 July 2014 Rich Griffin Silica EMEA later on in this workshop will need to be modified using your own skills. Simulink is a block diagram environment for multidomain simulation and Model-Based Design.

2

Right-click on the white background of the Diagram tab and choose Add IP.

. 8 Channel USB GPIO Module With Analog Inputs. Click on Run Block Automation to connect the Zynq PS with the memory. BittWare 250-SoC Xilinx Zynq UltraScale XCZU19EG BittWare XUP-P3R Xilinx Virtex UltraScale XCVU9P Intel Stratix 10 MX dev kit Intel Stratix 10 MX 2100.

Click Next several times until you see the Default Part screen. It supports system-level design simulation automatic code generation and continuous test and verification of embedded systems. DPU Top-level Block Diagram The DPU IP can be implemented in the programmable logic PL of the selected Zynq UltraScale MPSoC device with direct connections to the processing system PS.

Block Diagram Click on image to enlarge. The board contains all the necessary interfaces and supporting functions to enable a wide range of applications. From the list of IPs choose ZYNQ7 Processing System this is the Zynq PS and double-click on it.

4在 Diagram 界面里点击Run Block Automation完成对 ZYNQ7 Processing System IP核的配置生成外部 ZYNQ 系统的外部链接 IO 管脚. The primary goal of this TRD is to demonstrate the capabilities of the VCU core which is an integrated hard block present in Zynq UltraScale MPSoC EV devices. Simulink provides a graphical editor customizable block libraries and solvers for modeling and simulating dynamic systems.

Styx Xilinx Zynq FPGA Module 9 Tagus Artix 7 PCI Express Development Board 3 Telesto MAX 10 FPGA Module 5 Tenagra FPGA System Management Software 3 Theia Android Application 1 USB GPIO Modules 2 USB Relay Modules 1 Vivado Design Suit 4 Waxwing Spartan 6 FPGA Development Board 3 White Papers 1 Working With Xilinx. Enclosure 1099 3799. The USRP N321 is an all-in-one device that includes the Zynq-7100 SoC baseband processor two SFP ports a QSFP port a built-in GPSDO module and various other peripheral and synchronization features.

In the block diagram double click the AXI DMA block. Leave everything at the default values and click on OK. PCIe hard IP core.

新建一个vivado工程创建框图设计Block Design添加ZYNQ7 Processing System MIO配置添加QSPI Flash根据你的板子来设置引脚注意Bank0和Bank1的电平设置 MIO配置添加外设这里添加了一个以太网ENET0一个USB0SD0 和SD1分别是连接到SD卡和eMMCUART1被选中它将被. Click the Boards option in the Specify area. Un-tick the Enable Control Status Stream option and click OK.

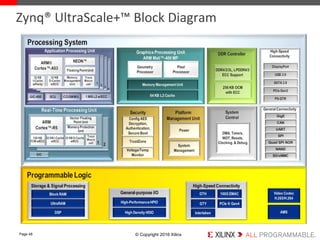

EG Block Diagram EV Block Diagram Heterogeneous Processing for Whole Application Acceleration. Multiple processing engines enable the optimization of functions across an. Block Diagram USRP N320N321.

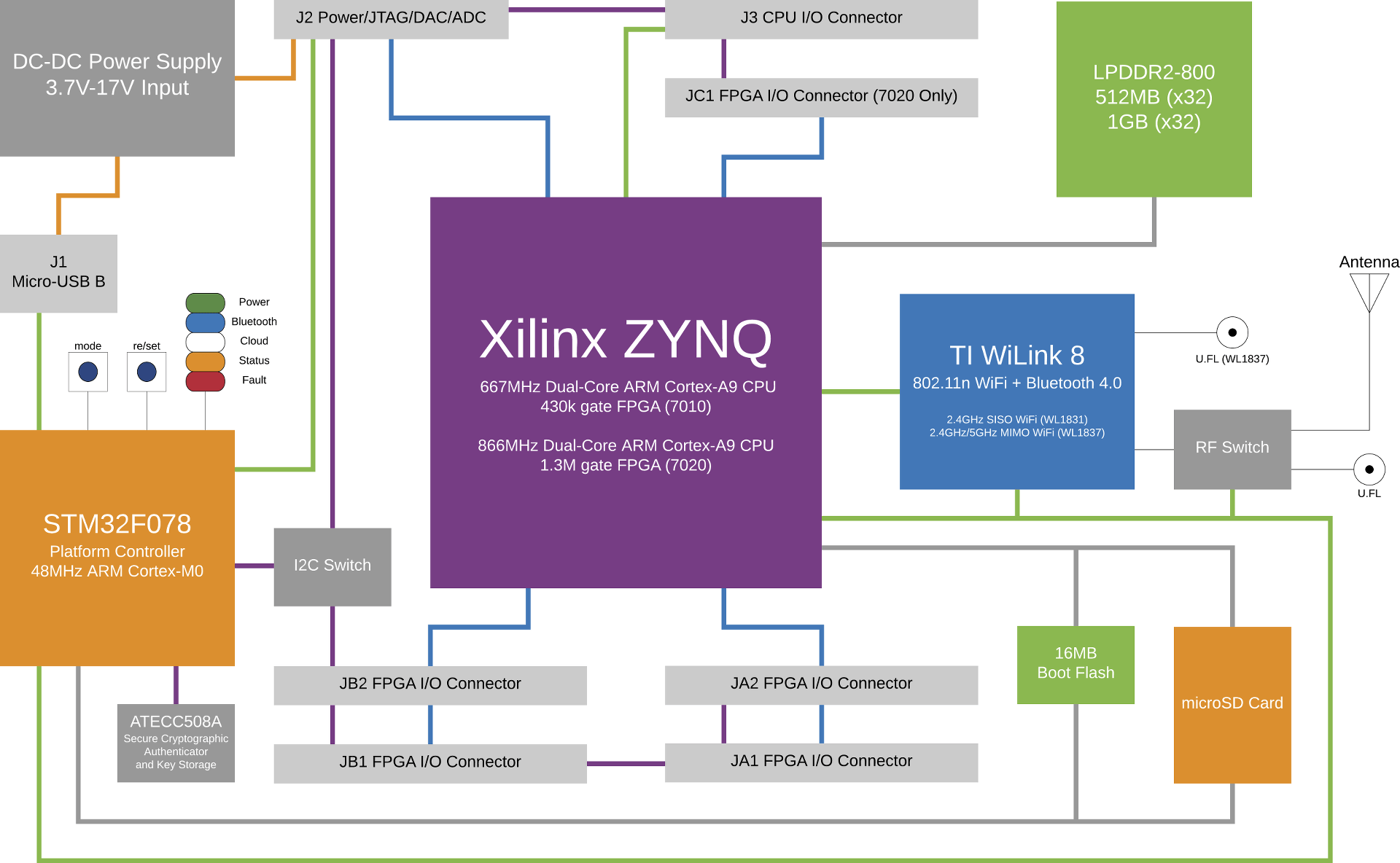

Click on image to enlarge. The Zynq family is based on the Xilinx All Programmable System-on-Chip AP SoC architecture which tightly integrates a dual-core ARM Cortex-A9 processor with Xilinx 7-series Field Programmable Gate. Zybo Z7 Reference Manual The Zybo Z7 is a feature-rich ready-to-use embedded software and digital circuit development board built around the Xilinx Zynq-7000 family.

ZYNQ开发学习笔记一BOOTbinfsbl文件将程序固化到板上的QSPI_Flash中 文章目录ZYNQ开发学习笔记一BOOTbinfsbl文件将程序固化到板上的QSPI_Flash中1环境介绍2正文vivado工程方面vitis工程方面3参考文献 1环境介绍 ZYNQ-7000 MZ7XA板卡. Chevrolet s10 fiche technique. 8 TTL compatible GPIOs available.

While in production the Series S-10 which was sold with the trim package DeLuxe was DeSotos entry-level car and was offered primarily as two-door and four-door sedans while the Custom offered upscale interiors and appearance. Choose Zynq-7000 from the. You can now see the Zynq PS in the block diagram.

ZedBoard is a complete development kit for designers interested in exploring designs using the AMD Xilinx Zynq-7000 All Programmable SoC. Block diagram of the Corundum NIC. Connect the DMA interrupts to the PS.

Block Diagram Description Applications. The DeSoto Series S-10 is an automobile produced by DeSoto from 1942 through to the 1952 model year. The DPU requires instructions to implement a neural network and accessible memory locations for input images as well as temporary and output data.

6 Analog input channels Multiplexed with GPIOs with 10-Bit. Based on the Xilinx UltraScale MPSoC architecture the Zynq UltraScale MPSoCs enable extensive system level differentiation integration and flexibility through hardware. Zynq-7000S devices feature a single-core ARM Cortex-A9 processor mated with 28nm Artix-7 based programmable logic representing the lowest.

The TRD serves as a platform for the user to tune the performance parameters of VCU and arrives at an optimal configuration for encoder and decoder blocks for their specific use case. USRP N310 Motherboard. USRP N310 ZYNQ-7100 4 CHANNELS 10 MHZ - 6 GHZ 10 GIGE The USRP N310 is a networked software defined radio that provides reliability and fault-tolerance for deployment in large-scale and distributed wireless systems.

Description Block diagram FAQ Resources Sample Code Specifications. Our software application will test the DMA in polling mode but to be able to use it in interrupt mode we need to connect the interrupts mm2s_introut and s2mm_introut to the Zynq PS.

Snickerdoodle Xilinx Zynq Arm Fpga Board Starts At 55 Crowdfunding Cnx Software

I Mx 8m Quad Quadlite Dual Smarc Som Iwave Systems

Xilinx Zynq 7000 Myc C7z015 Cpu Module Function Block Diagram Design Solutions Linux Solutions

I Mx 8m Plus Smarc Som Iwave Systems

Xilinx Zynq 7000 Myd C7z015 Development Board Function Block Diagram Development Development Board Design Solutions

I Mx 8m Plus Pico Itx Sbc Iwave Systems

Telecommunications

How To Understand The Term Clock Region In Xilinx Fpga Quora

Layerscape Ls1021a Smarc Som Iwave Systems

Software Hardware Co Design Using Xilinx Zynq Soc

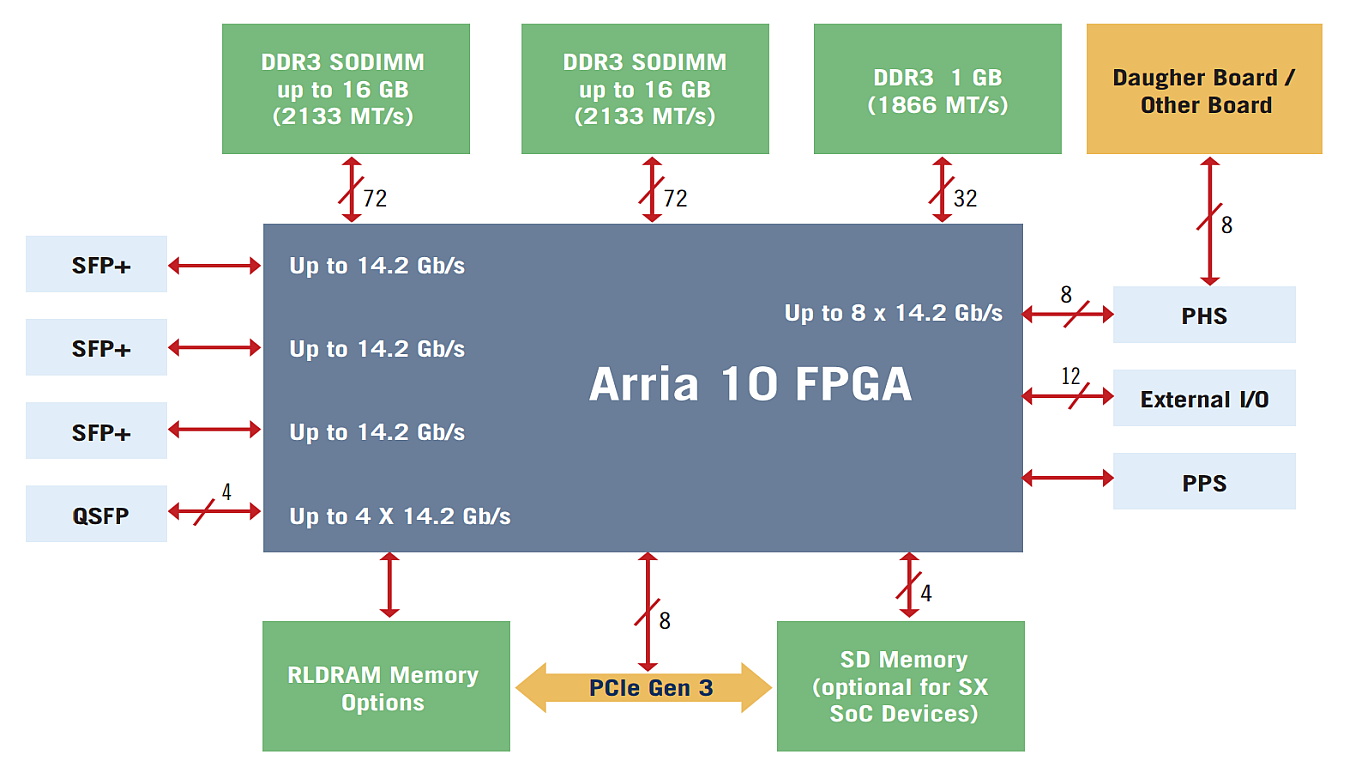

Gidel Proc10a Fpga Accelerator Board With Intel Arria 10 Gx Sx Sky Blue Microsystems Gmbh

Fpgas Fpga Cpu News

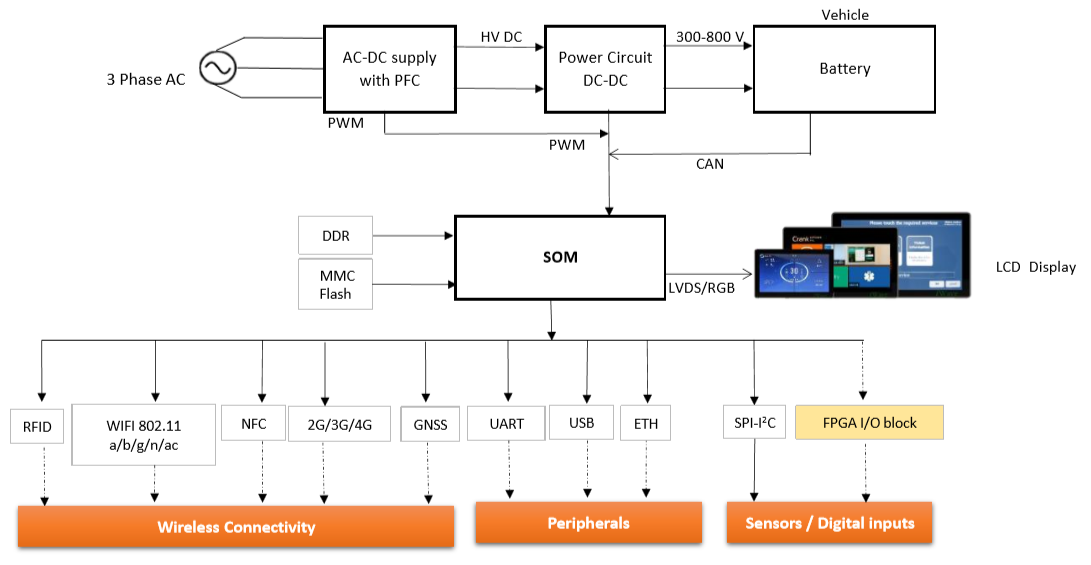

Advanced And Scalable Som Hmi Solutions For Ev Charging Station By Aslam Mohammed Medium

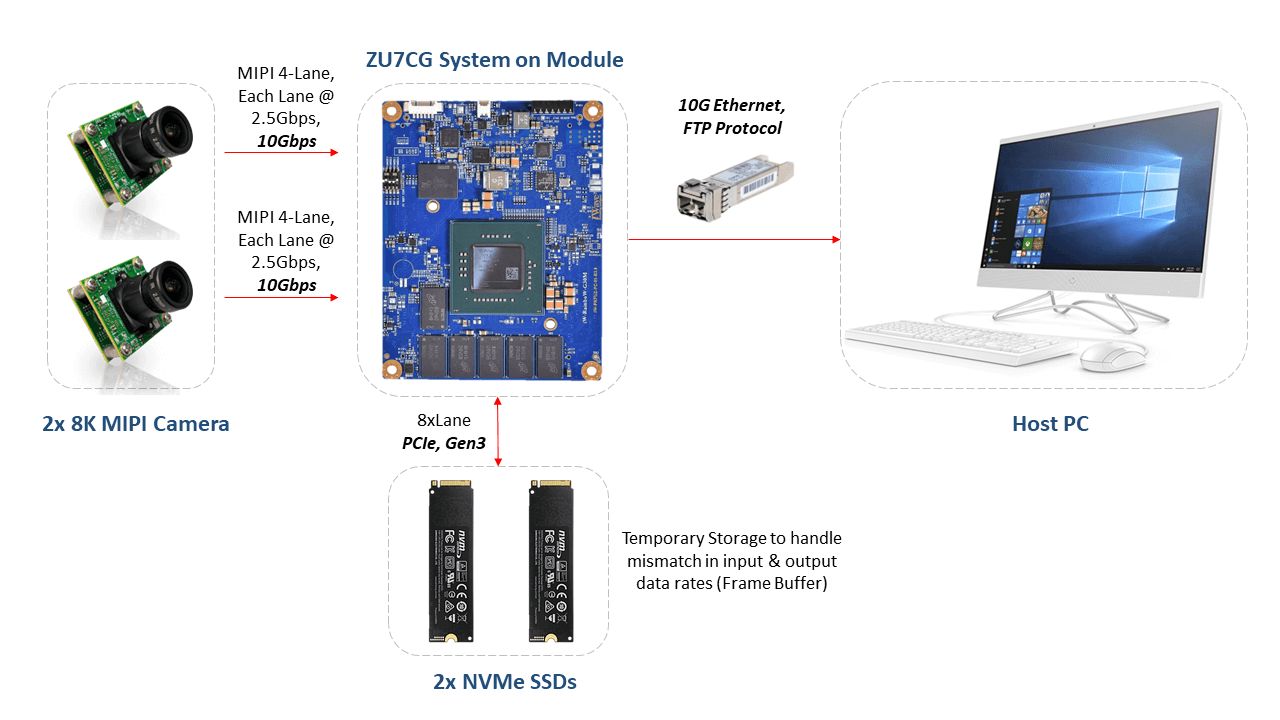

Case Study Designing Ultra Hd Image Acquisition System Using Zynq Ultrascale Mpsoc Devices For Medical Imaging Iwave Systems

Snickerdoodle Xilinx Zynq Arm Fpga Board Starts At 55 Crowdfunding Cnx Software

Fpga Soc Teknologi I Dag Og I Fremtiden

Ku19p Fpga System On Module Iwave Systems